# **Design and Evaluation of the Hamal Parallel Computer**

by

### J.P. Grossman

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

### December 2002

© Massachusetts Institute of Technology. All rights reserved.

| Author:       |                                                           |

|---------------|-----------------------------------------------------------|

|               | Department of Electrical Engineering and Computer Science |

|               | December 10, 2002                                         |

|               |                                                           |

|               |                                                           |

| Certified by: |                                                           |

| •             | Thomas F. Knight, Jr.                                     |

|               | Senior Research Scientist                                 |

|               | Thesis Supervisor                                         |

|               |                                                           |

|               |                                                           |

| Accepted by:  |                                                           |

| •             | Arthur C. Smith                                           |

|               | Chairman, Department Committee on Graduate Students       |

# Design and Evaluation of the Hamal Parallel Computer

by

### J.P. Grossman

Submitted to the Department of Electrical Engineering and Computer Science on December 10, 2002, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

## **Abstract**

Parallel shared-memory machines with hundreds or thousands of processor-memory nodes have been built; in the future we will see machines with millions or even billions of nodes. Associated with such large systems is a new set of design challenges. Many problems must be addressed by an architecture in order for it to be successful; of these, we focus on three in particular. First, a scalable memory system is required. Second, the network messaging protocol must be fault-tolerant. Third, the overheads of thread creation, thread management and synchronization must be extremely low.

This thesis presents the complete system design for *Hamal*, a shared-memory architecture which addresses these concerns and is directly scalable to one million nodes. Virtual memory and distributed objects are implemented in a manner that requires neither inter-node synchronization nor the storage of globally coherent translations at each node. We develop a lightweight fault-tolerant messaging protocol that guarantees message delivery and idempotence across a discarding network. A number of hardware mechanisms provide efficient support for massive multithreading and fine-grained synchronization.

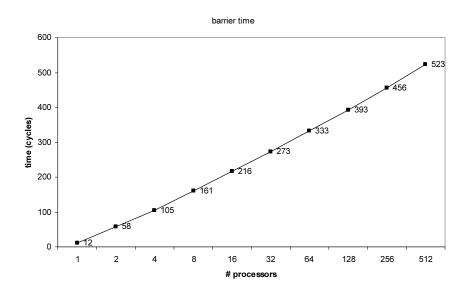

Experiments are conducted in simulation, using a trace-driven network simulator to investigate the messaging protocol and a cycle-accurate simulator to evaluate the Hamal architecture. We determine implementation parameters for the messaging protocol which optimize performance. A discarding network is easier to design and can be clocked at a higher rate, and we find that with this protocol its performance can approach that of a non-discarding network. Our simulations of Hamal demonstrate the effectiveness of its thread management and synchronization primitives. In particular, we find *register-based synchronization* to be an extremely efficient mechanism which can be used to implement a software barrier with a latency of only 523 cycles on a 512 node machine.

Thesis Supervisor: Thomas F. Knight, Jr.

Title: Senior Research Scientist

# **Acknowledgements**

It was an enormous privilege to work with Tom Knight, without whom this thesis would not have been possible. Tom is one of those rare supervisors that students actively seek out because of his broad interests and willingness to support the most strange and wonderful research. I know I speak on behalf of the entire Aries group when I thank him for all of his support, ideas, encouragement, and stories. We especially liked the stories.

I would like to thank my thesis committee – Tom Knight, Anant Agarwal and Krste Asanović – for their many helpful suggestions. Additional thanks to Krste for his careful reading and numerous detailed corrections.

I greatly enjoyed working with all members of Project Aries, past and present. Thanks in particular to Jeremy Brown and Andrew "bunnie" Huang for countless heated discussions and productive brainstorming sessions.

The Hamal *hash* function was developed with the help of Levente Jakab, who learned two months worth of advanced algebra in two weeks in order to write the necessary code.

A big thanks to Anthony Zolnik for providing much-needed administrative life-support to myself and Tom's other graduate students over the past few years.

Thanks to my parents for their endless love and support throughout my entire academic career, from counting bananas to designing parallel computers.

Finally, I am eternally grateful to my wife, Shana Nichols, for her incredible support and encouragement over the years. Many thanks for your help with proofreading parts of this thesis, and for keeping me sane.

The work in this thesis was supported by DARPA/AFOSR Contract Number F306029810172.

# **Contents**

| Chapter    | 1 - Introduction                                    | 11 |

|------------|-----------------------------------------------------|----|

| 1.1 I      | Designing for the Future                            | 12 |

| 1.2        | Гhe Hamal Parallel Computer                         | 13 |

| 1.3        | Contributions                                       | 14 |

| 1.4        | Omissions                                           | 14 |

| 1.5        | Organization                                        | 15 |

| Part I - I | Design                                              | 17 |

| Chapter    | 2 - Overview                                        | 19 |

| 2.1 I      | Design Principles                                   | 19 |

| 2.1.1      | Scalability                                         |    |

| 2.1.2      | Silicon Efficiency                                  | 19 |

| 2.1.3      | Simplicity                                          | 21 |

| 2.1.4      | Programmability                                     | 21 |

| 2.1.5      | Performance                                         | 21 |

| 2.2        | System Description                                  | 21 |

| Chapter    | 3 - The Memory System                               | 23 |

|            | Capabilities                                        |    |

| 3.1.1      | Segment Size and Block Index                        |    |

| 3.1.2      | Increment and Decrement Only                        |    |

| 3.1.3      | Subsegments                                         |    |

| 3.1.4      | Other Capability Fields                             |    |

| 3.2 I      | Forwarding Pointer Support                          |    |

| 3.2.1      | Object Identification and Squids                    |    |

| 3.2.2      | Pointer Comparisons and Memory Operation Reordering |    |

| 3.2.3      | Implementation                                      |    |

| 3.3 A      | Augmented Memory                                    |    |

| 3.3.1      | Virtual Memory                                      |    |

| 3.3.2      | Automatic Page Allocation                           | 31 |

| 3.3.3      | Hardware LRU                                        | 31 |

| 3.3.4      | Atomic Memory Operations                            | 31 |

| 3.3.5      | Memory Traps and Forwarding Pointers                |    |

| 3.4 I      | Distributed Objects                                 |    |

| 3.4.1      | Extended Address Partitioning                       |    |

| 3.4.2      | Sparsely Faceted Arrays                             |    |

| 3.4.3      | Comparison of the Two Approaches                    |    |

| 3.4.4      | Data Placement                                      |    |

| 3.5 N      | Memory Semantics                                    | 36 |

| Chap       | ter 4 - Processor Design                              | 37 |

|------------|-------------------------------------------------------|----|

| 4.1        | Datapath Width and Multigranular Registers            | 37 |

| 4.2        | Multithreading and Event Handling                     |    |

| 4.3        | Thread Management                                     | 39 |

| 4.         | 3.1 Thread Creation                                   | 39 |

| 4.         | 3.2 Register Dribbling and Thread Suspension          | 39 |

| 4.4        | Register-Based Synchronization                        | 40 |

| 4.5        | Shared Registers                                      | 40 |

| 4.6        | Hardware Hashing                                      |    |

|            | 6.1 A Review of Linear Codes                          |    |

|            | 6.2 Constructing Hash Functions from Linear Codes     |    |

|            | 6.3 Nested BCH Codes                                  |    |

|            | 6.4 Implementation Issues                             |    |

|            | 6.5 The Hamal <i>hash</i> Instruction                 |    |

| 4.7        |                                                       |    |

|            | 7.1 Hardware LRU                                      |    |

| 4.         | 7.2 Miss Bits                                         | 46 |

| Chan       | ter 5 - Messaging Protocol                            | 47 |

| 5.1        | Previous Work                                         |    |

| 5.2        | Basic Requirements                                    |    |

| 5.3        | Out of Order Messages                                 |    |

| 5.4        | Message Identification                                |    |

| 5.5        | Hardware Requirements                                 |    |

|            | •                                                     |    |

| _          | ter 6 - The Hamal Microkernel                         | 53 |

| 6.1        | Page Management                                       |    |

| 6.2        | Thread Management                                     |    |

| 6.3        | Sparsely Faceted Arrays                               |    |

| 6.4<br>6.5 | Kernel Calls                                          |    |

|            | Forwarding Pointers                                   |    |

| 6.6<br>6.7 | UV TrapsBoot Sequence                                 |    |

| 0.7        | Boot Sequence                                         |    |

| Chap       | ter 7 - Deadlock Avoidance                            | 57 |

| 7.1        | Hardware Queues and Tables                            | 58 |

| 7.2        | Intra-Node Deadlock Avoidance                         | 59 |

| 7.3        | Inter-Node Deadlock Avoidance                         | 60 |

| Part I     | I - Evaluation                                        | 63 |

| Chap       | ter 8 - Simulation                                    | 65 |

| 8.1        | An Efficient C++ Framework for Cycle-Based Simulation | 65 |

| 8.         | 1.1 The Sim Framework                                 | 66 |

| 8.         | 1.2 Timestamps                                        |    |

|            | 1.3 Other Debugging Features                          |    |

|            | 1.4 Performance Evaluation                            |    |

| 8.         | 1.5 Comparison with SystemC                           | 70 |

| 8.1.6 Discussion                                                 | 71           |

|------------------------------------------------------------------|--------------|

| 8.2 The Hamal Simulator                                          | 72           |

| 8.2.1 Processor-Memory Nodes                                     | 73           |

| 8.2.2 Network                                                    | 73           |

| 8.3 Development Environment                                      | 75           |

| Chapter 9 - Parallel Programming                                 | 77           |

| 9.1 Processor Sets                                               | 77           |

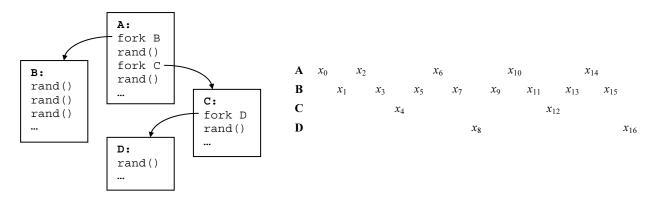

| 9.2 Parallel Random Number Generation                            | 78           |

| 9.2.1 Generating Multiple Streams                                | 78           |

| 9.2.2 Dynamic Sequence Partitioning                              |              |

| 9.2.3 Random Number Generation in Hamal                          |              |

| 9.3 Benchmarks                                                   |              |

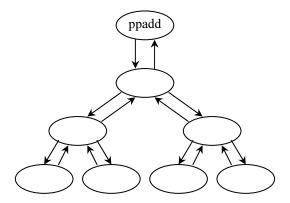

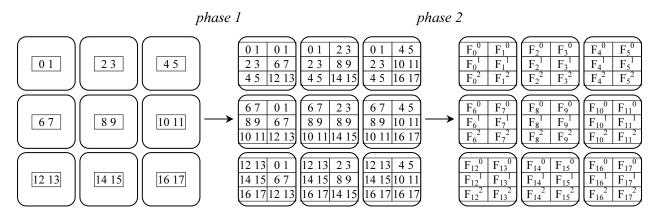

| 9.3.1 Parallel Prefix Addition                                   |              |

| 9.3.2 Quicksort                                                  |              |

| 9.3.3 <i>N</i> -Body Simulation                                  |              |

| 9.3.4 Counting Words                                             | 82           |

| Chapter 10 - Synchronization                                     | 83           |

| 10.1 Atomic Memory Operations                                    | 83           |

| 10.2 Shared Registers                                            | 84           |

| 10.3 Register-Based Synchronization                              | 84           |

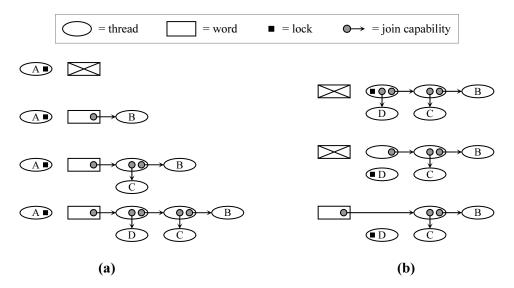

| 10.4 UV Trap Bits                                                | 87           |

| 10.4.1 Producer-Consumer Synchronization                         |              |

| 10.4.2 Locks                                                     | 89           |

| Chapter 11 - The Hamal Processor                                 | 93           |

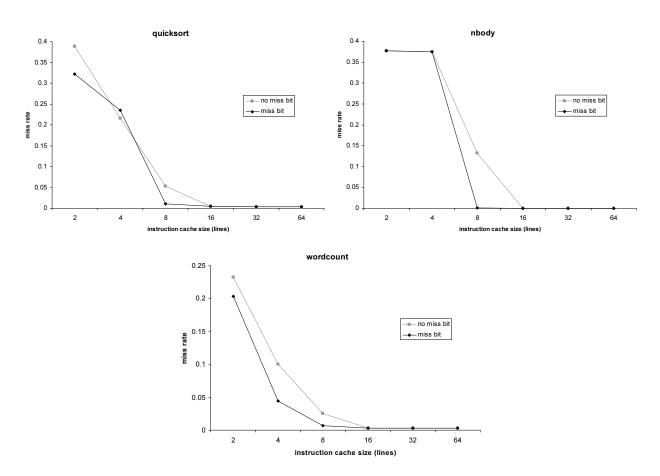

| 11.1 Instruction Cache Miss Bits                                 | 93           |

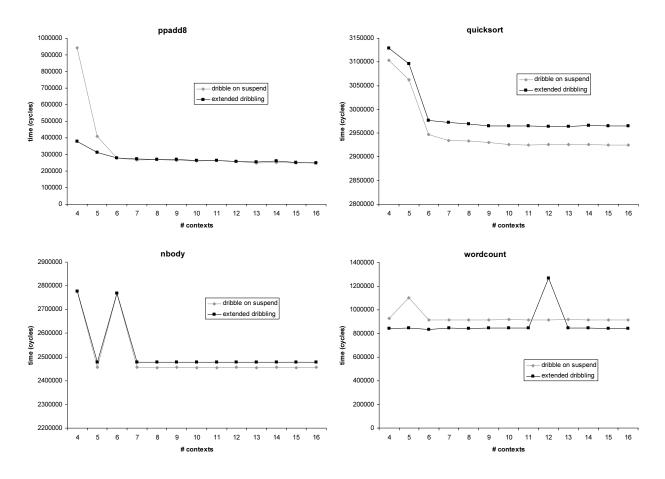

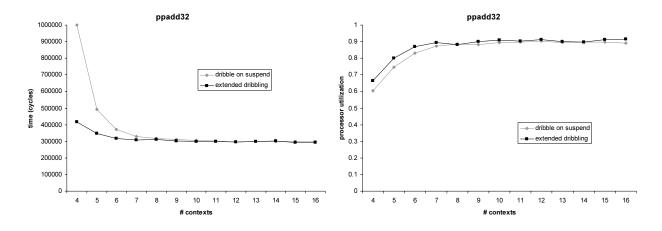

| 11.2 Register Dribbling                                          | 95           |

| Chapter 12 - Squids                                              | 97           |

| 12.1 Benchmarks                                                  | 97           |

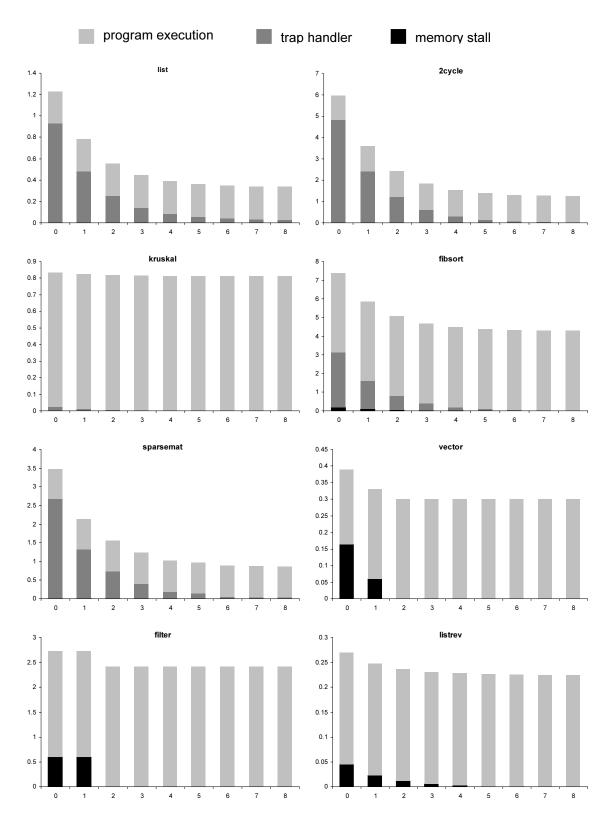

| 12.2 Simulation Results                                          |              |

| 12.3 Extension to Other Architectures                            | 101          |

| 12.4 Alternate Approaches                                        | 101          |

| 12.4.1 Generation Counters                                       | 101          |

| 12.4.2 Software Comparisons                                      | 102          |

| 12.4.3 Data Dependence Speculation                               |              |

| 12.4.4 Squids without Capabilities                               | 103          |

| 12.5 Discussion                                                  | 103          |

| Chapter 13 - Analytically Modelling a Fault-Tolerant Messaging I | Protocol 105 |

| 13.1 Motivating Problem                                          |              |

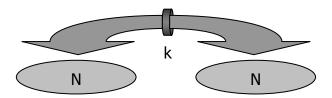

| 13.2 Crossbar Network                                            |              |

| 13.2.1 Circuit Switched Crossbar                                 |              |

| 13.2.2 Wormhole Routed Crossbar                                  |              |

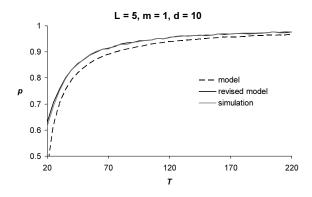

| 13.2.3 Comparison with Simulation                                | 108          |

| 13.2.4 Improving the Model                                       |              |

| 13.3.1       Circuit Switched Network       112         13.3.2       Wormhole Routed Network       112         13.3.3       Multiple Solutions       113         13.4       Multistage Interconnection Networks       114         13.5       Butterfly Network       116         Chapter 14 - Evaluation of the Idempotent Messaging Protocol       119         14.1       Simulation Environment       119         14.1.1       Hardware Model       119         14.1.2       Block Structured Traces       119         14.1.3       Obtaining the Traces       120         14.1.4       Synchronization       122         14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.1.7       Micro-Benchmarks       123         14.1.8       Send Table Size       124         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132                                                                           | 13.3    | Bisection-Limited Network                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------|-----|

| 13.3.3       Multiple Solutions       113         13.3.4       Comparing the Routing Protocols       114         13.4       Multistage Interconnection Networks       114         13.5       Butterfly Network       116         Chapter 14 - Evaluation of the Idempotent Messaging Protocol       119         14.1       Simulation Environment       119         14.1.1       Hardware Model       119         14.1.2       Block Structured Traces       119         14.1.3       Obtaining the Traces       120         14.1.4       Synchronization       122         14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136                                                                            | 13.3    |                                                       |     |

| 13.3.4 Comparing the Routing Protocols       114         13.4 Multistage Interconnection Networks       114         13.5 Butterfly Network       116         Chapter 14 - Evaluation of the Idempotent Messaging Protocol       119         14.1 Simulation Environment       119         14.1.1 Hardware Model       119         14.1.2 Block Structured Traces       119         14.1.3 Obtaining the Traces       120         14.1.4 Synchronization       122         14.1.5 Micro-Benchmarks       123         14.1.6 Trace-Driven Simulator       123         14.2 Packet Retransmission       124         14.3 Send Table Size       127         14.4 Network Buffering       128         14.5 Receive Table Size       130         14.6 Channel Width       131         14.7 Performance Comparison: Discarding vs. Non-Discarding       135         15.1 Parallel Prefix Addition       135         15.2 Quicksort       136         15.3 N-body Simulation       135         15.4 Wordcount       138         15.5 Multiprogramming       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2 Fault-Tolerant Messaging Protocol       142<                  | 13.3    |                                                       |     |

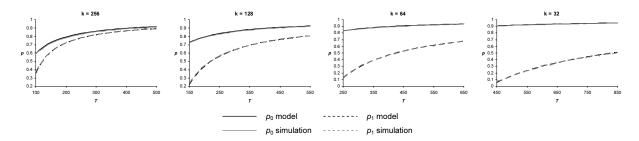

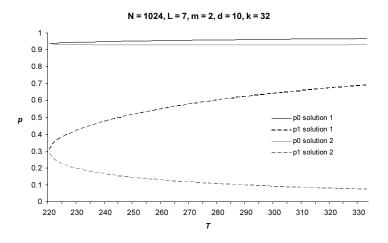

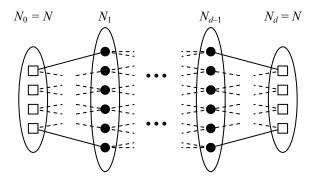

| 13.4       Multistage Interconnection Networks       114         13.5       Butterfly Network       116         Chapter 14 - Evaluation of the Idempotent Messaging Protocol       119         14.1       Simulation Environment       119         14.1.1       Hardware Model       119         14.1.2       Block Structured Traces       119         14.1.3       Obtaining the Traces       120         14.1.4       Synchronization       122         14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5 <td< td=""><td>13.3</td><td>.3 Multiple Solutions</td><td>113</td></td<>                 | 13.3    | .3 Multiple Solutions                                 | 113 |

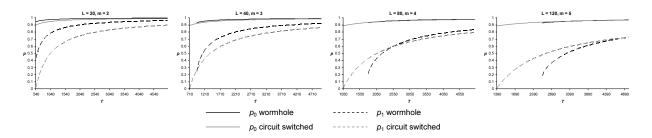

| 13.5   Butterfly Network   116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13.3    | .4 Comparing the Routing Protocols                    | 114 |

| Chapter 14 - Evaluation of the Idempotent Messaging Protocol         119           14.1 Simulation Environment         119           14.1.1 Hardware Model         119           14.1.2 Block Structured Traces         119           14.1.3 Obtaining the Traces         120           14.1.4 Synchronization         122           14.1.5 Micro-Benchmarks         123           14.1.6 Trace-Driven Simulator         123           14.2 Packet Retransmission         124           14.3 Send Table Size         127           14.4 Network Buffering         128           14.5 Receive Table Size         130           14.6 Channel Width         131           14.7 Performance Comparison: Discarding vs. Non-Discarding         132           15.1 Parallel Prefix Addition         135           15.2 Quicksort         136           15.3 N-body Simulation         137           15.4 Wordcount         138           15.5 Multiprogramming         139           15.6 Discussion         139           15.6 Discussion         141           16.1 Memory System         141           16.2 Fault-Tolerant Messaging Protocol         142           16.3 Thread Management         142           16.5 Improving th | 13.4    | Multistage Interconnection Networks                   | 114 |

| 14.1 Simulation Environment       119         14.1.1 Hardware Model       119         14.1.2 Block Structured Traces       119         14.1.3 Obtaining the Traces       120         14.1.4 Synchronization       122         14.1.5 Micro-Benchmarks       123         14.1.6 Trace-Driven Simulator       123         14.2 Packet Retransmission       124         14.3 Send Table Size       127         14.4 Network Buffering       128         14.5 Receive Table Size       130         14.6 Channel Width       131         14.7 Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1 Parallel Prefix Addition       135         15.2 Quicksort       136         15.3 N-body Simulation       137         15.4 Wordcount       138         15.5 Multiprogramming       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.5 I Memory Streaming       143         16.5.1 Memory Streaming                                                      | 13.5    | Butterfly Network                                     | 116 |

| 14.1.1 Hardware Model.       119         14.1.2 Block Structured Traces.       119         14.1.3 Obtaining the Traces.       120         14.1.4 Synchronization.       122         14.1.5 Micro-Benchmarks.       123         14.1.6 Trace-Driven Simulator.       123         14.2 Packet Retransmission.       124         14.3 Send Table Size.       127         14.4 Network Buffering       128         14.5 Receive Table Size       130         14.6 Channel Width.       131         14.7 Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation         15.1 Parallel Prefix Addition.       135         15.2 Quicksort.       136         15.3 N-body Simulation       137         15.4 Wordcount.       138         15.5 Multiprogramming       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5.1 Improving the Design       143         16.5.2 Security Issues with Register-Based Synchronization       143                                               | Chapte  |                                                       |     |

| 14.1.2       Block Structured Traces       119         14.1.3       Obtaining the Traces       120         14.1.4       Synchronization       122         14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.4       Synchronization       143 <td>14.1</td> <td>Simulation Environment</td> <td>119</td>                                     | 14.1    | Simulation Environment                                | 119 |

| 14.1.3       Obtaining the Traces       120         14.1.4       Synchronization       122         14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5.1       Memory Streaming       <                                                                                                     | 14.1    | .1 Hardware Model                                     | 119 |

| 14.1.4       Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14.1    | .2 Block Structured Traces                            | 119 |

| 14.1.5       Micro-Benchmarks       123         14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Sc                                                                                    | 14.1    | .3 Obtaining the Traces                               | 120 |

| 14.1.6       Trace-Driven Simulator       123         14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Re                                                                                                            | 14.1    | .4 Synchronization                                    | 122 |

| 14.2       Packet Retransmission       124         14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5       I Memory Streaming       143         16.5       Security Issues with Register-Based Synchronization       143         16.5       Thread Scheduling and Synchronization       144         16.6 <t< td=""><td>14.1</td><td>.5 Micro-Benchmarks</td><td>123</td></t<>                    | 14.1    | .5 Micro-Benchmarks                                   | 123 |

| 14.3       Send Table Size       127         14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                | 14.1    | .6 Trace-Driven Simulator                             | 123 |

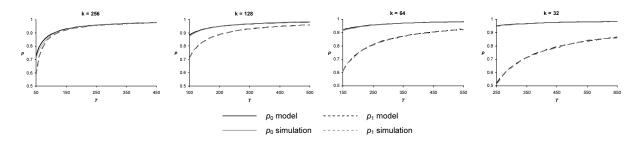

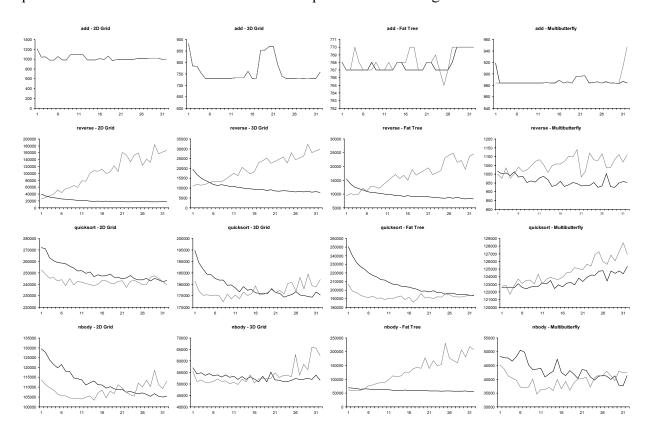

| 14.4       Network Buffering       128         14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                  | 14.2    | Packet Retransmission                                 | 124 |

| 14.5       Receive Table Size       130         14.6       Channel Width       131         14.7       Performance Comparison: Discarding vs. Non-Discarding       132         Chapter 15 - System Evaluation       135         15.1       Parallel Prefix Addition       135         15.2       Quicksort       136         15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                 | 14.3    | Send Table Size                                       | 127 |

| 14.6       Channel Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14.4    | Network Buffering                                     | 128 |

| 14.7 Performance Comparison: Discarding vs. Non-Discarding.       132         Chapter 15 - System Evaluation       135         15.1 Parallel Prefix Addition.       135         15.2 Quicksort.       136         15.3 N-body Simulation       137         15.4 Wordcount.       138         15.5 Multiprogramming.       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1 Memory System.       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management.       142         16.4 Synchronization.       143         16.5 Improving the Design.       143         16.5.1 Memory Streaming.       143         16.5.2 Security Issues with Register-Based Synchronization.       143         16.5.3 Thread Scheduling and Synchronization.       144         16.6 Summary.       144                                                                                                                                                                                                                                                                                                                                               | 14.5    | Receive Table Size                                    | 130 |

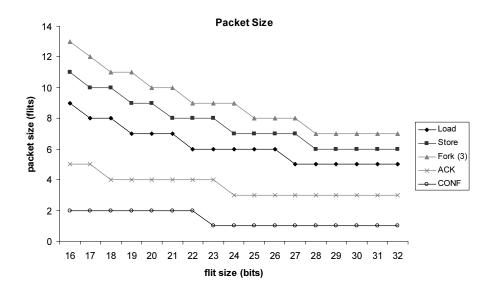

| Chapter 15 - System Evaluation       135         15.1 Parallel Prefix Addition       135         15.2 Quicksort       136         15.3 N-body Simulation       137         15.4 Wordcount       138         15.5 Multiprogramming       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5 Improving the Design       143         16.5.1 Memory Streaming       143         16.5.2 Security Issues with Register-Based Synchronization       143         16.5.3 Thread Scheduling and Synchronization       144         16.6 Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14.6    | Channel Width                                         | 131 |

| 15.1       Parallel Prefix Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14.7    | Performance Comparison: Discarding vs. Non-Discarding | 132 |

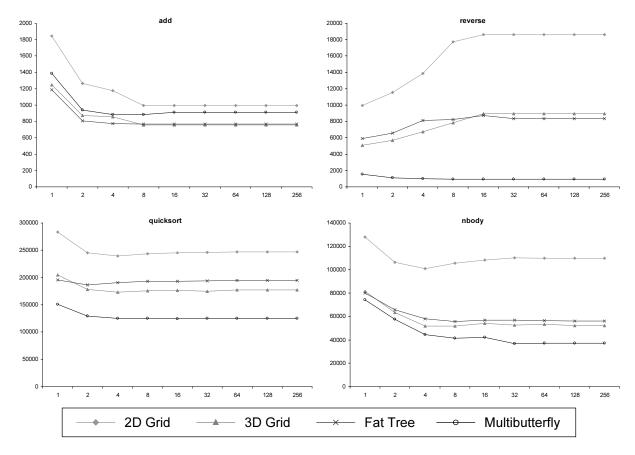

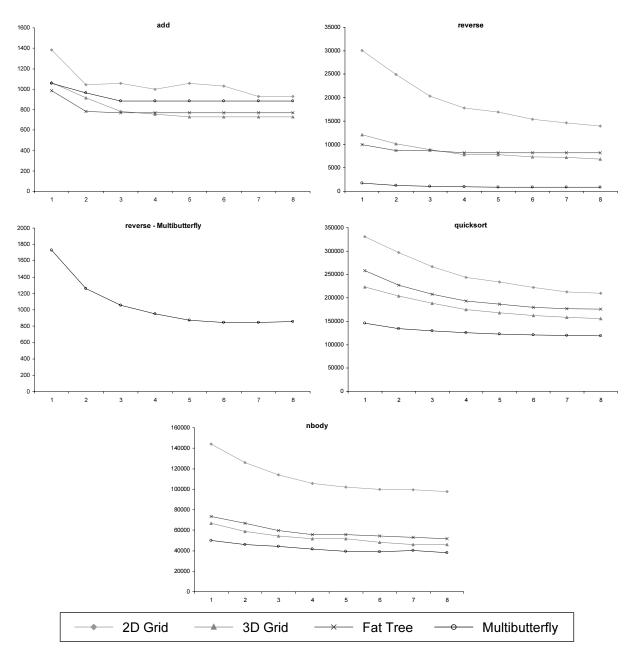

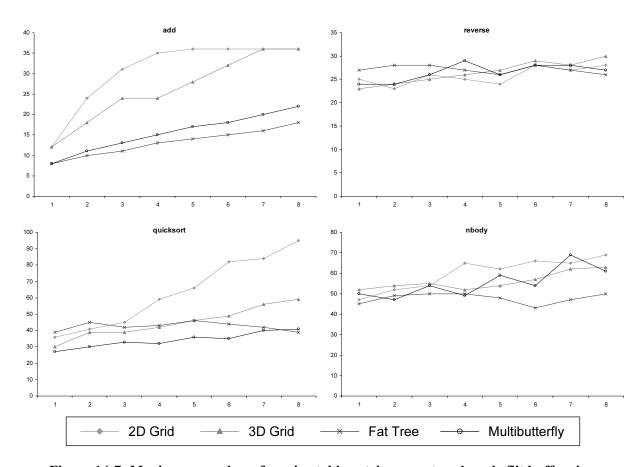

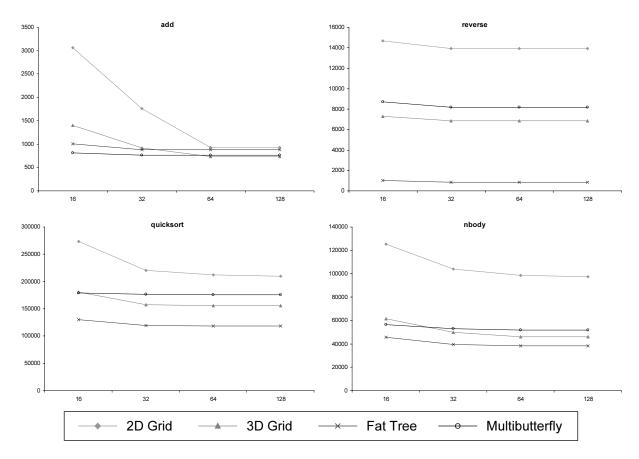

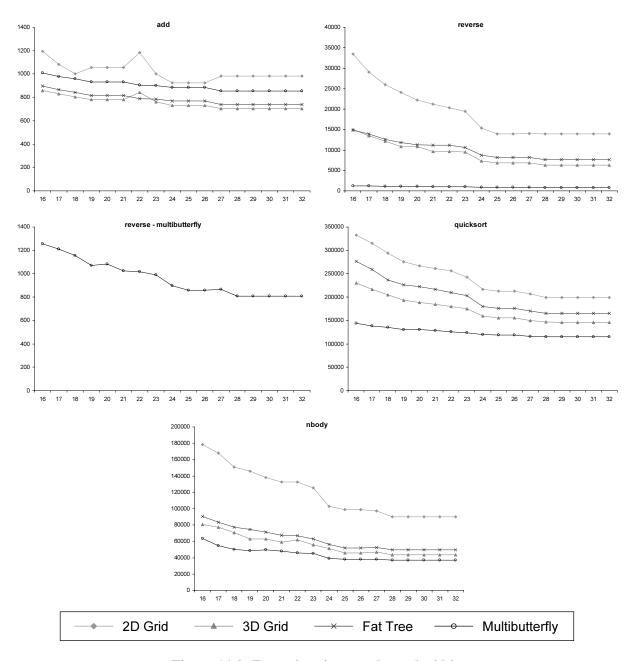

| 15.2 Quicksort       136         15.3 N-body Simulation       137         15.4 Wordcount       138         15.5 Multiprogramming       139         15.6 Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5 Improving the Design       143         16.5.1 Memory Streaming       143         16.5.2 Security Issues with Register-Based Synchronization       143         16.5.3 Thread Scheduling and Synchronization       144         16.6 Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Chapte  | r 15 - System Evaluation                              | 135 |

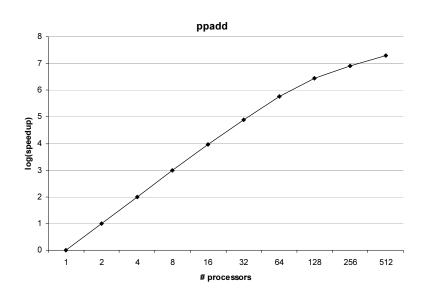

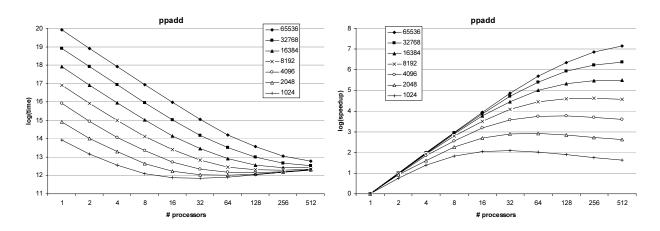

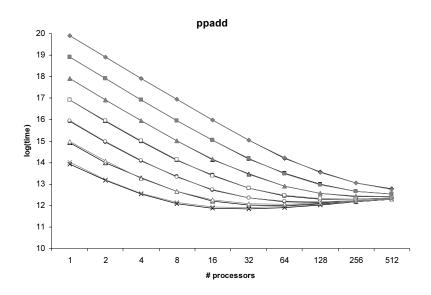

| 15.3       N-body Simulation       137         15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15.1    | Parallel Prefix Addition                              | 135 |

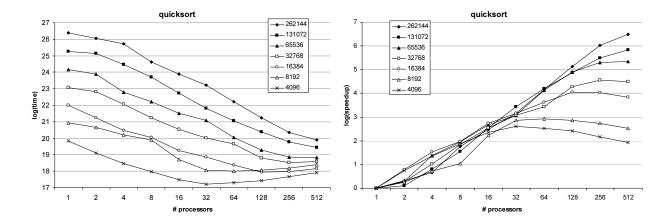

| 15.4       Wordcount       138         15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15.2    | Quicksort                                             | 136 |

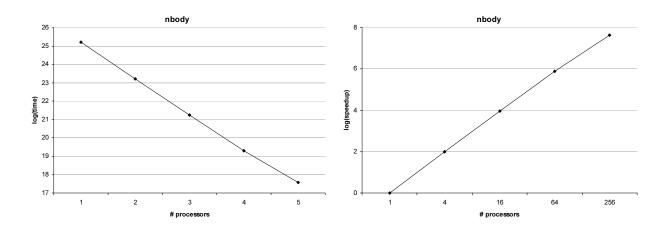

| 15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15.3    | <i>N</i> -body Simulation                             | 137 |

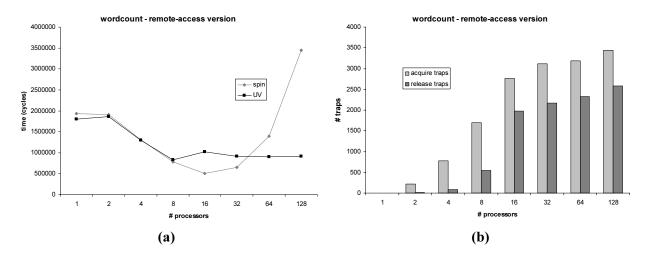

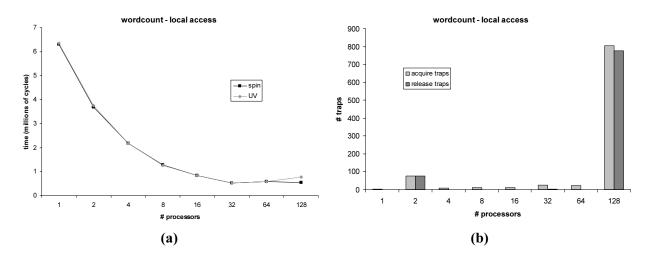

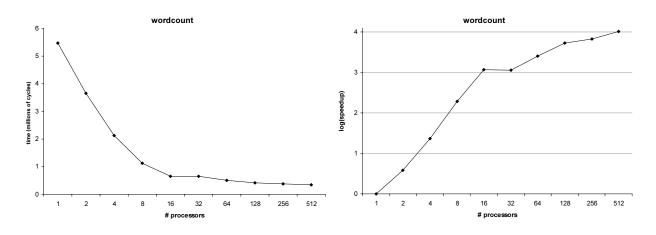

| 15.5       Multiprogramming       139         15.6       Discussion       139         Chapter 16 - Conclusions and Future Work       141         16.1       Memory System       141         16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15.4    | Wordcount                                             | 138 |

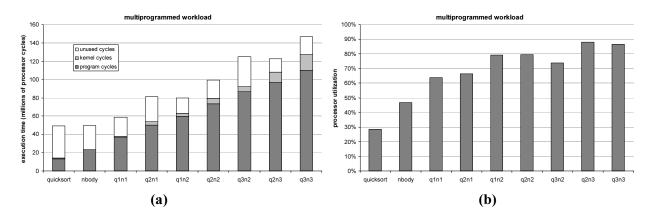

| Chapter 16 - Conclusions and Future Work       141         16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5 Improving the Design       143         16.5.1 Memory Streaming       143         16.5.2 Security Issues with Register-Based Synchronization       143         16.5.3 Thread Scheduling and Synchronization       144         16.6 Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15.5    |                                                       |     |

| 16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5 Improving the Design       143         16.5.1 Memory Streaming       143         16.5.2 Security Issues with Register-Based Synchronization       143         16.5.3 Thread Scheduling and Synchronization       144         16.6 Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15.6    | Discussion                                            | 139 |

| 16.1 Memory System       141         16.2 Fault-Tolerant Messaging Protocol       142         16.3 Thread Management       142         16.4 Synchronization       143         16.5 Improving the Design       143         16.5.1 Memory Streaming       143         16.5.2 Security Issues with Register-Based Synchronization       143         16.5.3 Thread Scheduling and Synchronization       144         16.6 Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Chapte  | r 16 - Conclusions and Future Work                    | 141 |

| 16.2       Fault-Tolerant Messaging Protocol       142         16.3       Thread Management       142         16.4       Synchronization       143         16.5       Improving the Design       143         16.5.1       Memory Streaming       143         16.5.2       Security Issues with Register-Based Synchronization       143         16.5.3       Thread Scheduling and Synchronization       144         16.6       Summary       144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       |                                                       | 141 |

| 16.3 Thread Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16.2    |                                                       |     |

| 16.4Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                       |     |

| 16.5Improving the Design14316.5.1Memory Streaming14316.5.2Security Issues with Register-Based Synchronization14316.5.3Thread Scheduling and Synchronization14416.6Summary144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                       |     |

| 16.5.1Memory Streaming14316.5.2Security Issues with Register-Based Synchronization14316.5.3Thread Scheduling and Synchronization14416.6Summary144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | •                                                     |     |

| 16.5.2Security Issues with Register-Based Synchronization14316.5.3Thread Scheduling and Synchronization14416.6Summary144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                       |     |

| 16.5.3 Thread Scheduling and Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                       |     |

| 16.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                       |     |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bibliog | •                                                     |     |

# **Chapter 1**

## Introduction

The last thing one knows when writing a book is what to put first.

- Blaise Pascal (1623-1662), "Pensées"

Over the years there has been an enormous amount of hardware research in parallel computation. It is a testament to the difficulty of the problem that despite the large number of wildly varying architectures which have been designed and evaluated, there are few agreed-upon techniques for constructing a good machine. Even basic questions such as whether or not remote data should be cached remain unanswered. This is in marked contrast to the situation in the scalar world, where many well-known hardware mechanisms are consistently used to improve performance (e.g. caches, branch prediction, speculative execution, out of order execution, superscalar issue, register renaming, etc.).

The primary reason that designing a parallel architecture is so difficult is that the parameters which define a "good" machine are extremely application-dependent. A simple physical simulation is ideal for a SIMD machine with a high processor to memory ratio and a fast 3D grid network, but will make poor utilization of silicon resources in a Beowulf cluster and will suffer due to increased communication latencies and reduced bandwidth. Conversely, a parallel database application will perform extremely well on the latter machine but will probably not even run on the former. Thus, it is important for the designer of a parallel machine to choose his or her battles early in the design process by identifying the target application space in advance.

There is an obvious tradeoff involved in choosing an application space. The smaller the space, the easier it is to match the hardware resources to those required by user programs, resulting in faster and more efficient program execution. Hardware design can also be simplified by omitting features which are unnecessary for the target applications. For example, the Blue Gene architecture [IBM01], which is being designed specifically to fold proteins, does not support virtual memory [Denneau00]. On the other hand, machines with a restricted set of supported applications are less useful and not as interesting to end users. As a result, they are not cost effective because they are unlikely to be produced in volume. Since not everyone has \$100 million to spend on a fast computer, there is a need for commodity general-purpose parallel machines.

The term "general-purpose" is broad and can be further subdivided into three categories. A machine is general-purpose at the *application* level if it supports arbitrary applications via a restricted programming methodology; examples include Blue Gene [IBM01] and the J-Machine ([Dally92], [Dally98]). A machine is general-purpose at the *language* level if it supports arbitrary programming paradigms in a restricted run-time environment; examples include the RAW machine [Waingold97] and Smart Memories [Mai00]. Finally, a machine is general-purpose at the *environment* level if it supports arbitrary management of computation, including resource

sharing between mutually non-trusting applications. This category represents the majority of parallel machines, such as Alewife [Agarwal95], Tera [Alverson90], The M-Machine ([Dally94b], [Fillo95]), DASH [Lenoski92], FLASH [Kuskin94], and Active Pages [Oskin98]. Note that each of these categories is not necessarily a sub-category of the next. For example, Active Pages are general-purpose at the environment level [Oskin99a], but not at the application level as only programs which exhibit regular, large-scale, fine-grained parallelism can benefit from the augmented memory pages.

The overall goal of this thesis is to investigate design principles for scalable parallel architectures which are general-purpose at the application, language and environment levels. Such architectures are inevitably less efficient than restricted-purpose hardware for any given application, but may still provide better performance at a fixed price due to the fact that they are more cost-effective. Focusing on general-purpose architectures, while difficult, is appealing from a research perspective as it forces one to consider mechanisms which support computation in a broad sense.

### 1.1 Designing for the Future

Parallel shared-memory machines with hundreds or thousands of processor-memory nodes have been built (e.g. [Dally98], [Laudon97], [Anderson97]); in the future we will see machines with millions [IBM01] and eventually billions of nodes. Associated with such large systems is a new set of design challenges; fundamental architectural changes are required to construct a machine with so many nodes and to efficiently support the resulting number of threads. Three problems in particular must be addressed. First, the memory system must be extremely scalable. In particular, it should be possible to both allocate and physically locate distributed objects without storing global information at each node. Second, the network messaging protocol must be fault-tolerant. With millions of discrete network components it becomes extremely difficult to prevent electrical or mechanical failures from corrupting packets, regardless of the fault-tolerant routing strategy that is used. Instead, the focus will shift to end-to-end messaging protocols that ensure packet delivery across an unreliable network. Finally, the hardware must provide support for efficient thread management. Fine-grained parallelism is required to effectively utilize millions of nodes. The overheads of thread creation, context switching and synchronization should therefore be extremely low.

At the same time, new fabrication processes that allow CMOS logic and DRAM to be placed on the same die open the door for novel hardware mechanisms and a tighter coupling between processors and memory. The simplest application of this technology is to augment existing processor architectures with low-latency high-bandwidth memory [Patterson97]. A more exciting approach is to augment DRAM with small amounts of logic to extend its capabilities and/or perform simple computation directly at the memory. Several research projects have investigated various ways in which this can be done (e.g. [Oskin98], [Margolus00], [Mai00], [Gokhale95]). However, none of the proposed architectures are general-purpose at both the application and the environment level, due to restrictions placed on the application space and/or the need to associate a significant amount of application-specific state with large portions of physical memory.

Massive parallelism and RAM integration are central to the success of future parallel architectures. In this thesis we will explore these issues in the context of general-purpose computation.

### 1.2 The Hamal Parallel Computer

The primary vehicle of our presentation will be the complete system design of a shared memory machine: The Hamal <sup>1</sup> Parallel Computer. Hamal integrates many new and existing architectural ideas with the specific goal of providing a massively scalable and easily programmable platform. The principal tool used in our studies is a flexible cycle-accurate simulator for the Hamal architecture. While many of the novel features of Hamal could be presented and evaluated in isolation, there are a number of advantages to incorporating them into a complete system and assessing them in this context. First, a full simulation ensures that no details have been omitted, so the true cost of each feature can be determined. Second, it allows us to verify that the features are mutually compatible and do not interact in undesirable or unforeseen ways. Third, the cycle-accurate simulator provides a consistent framework within which we can conduct our evaluations. Fourth, our results are more realistic as they are derived from a cycle-accurate simulation of a complete system.

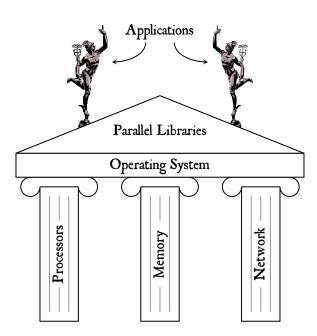

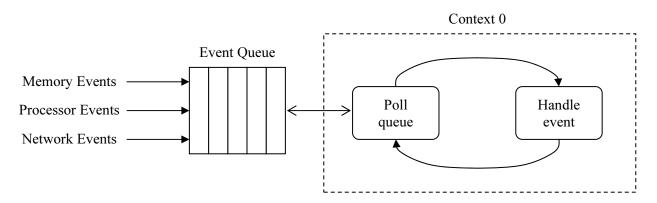

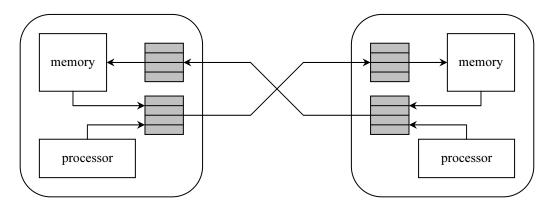

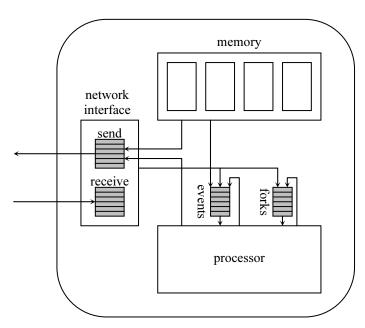

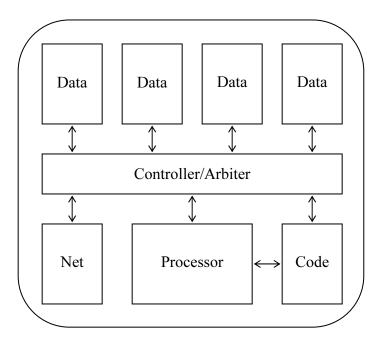

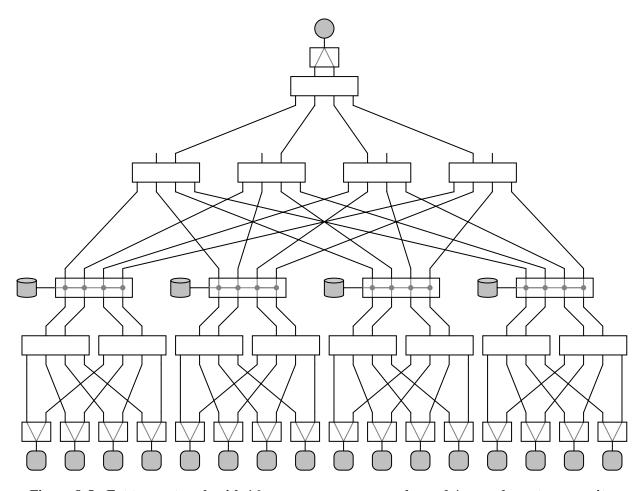

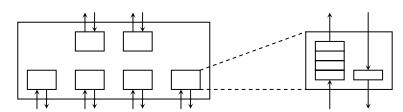

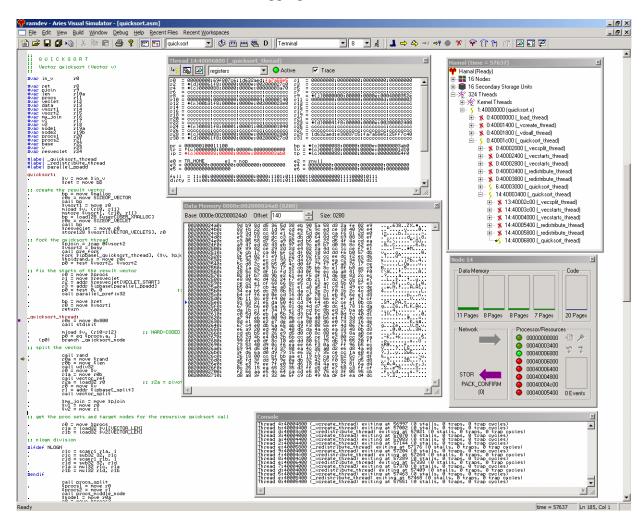

A fifth and final advantage to the full-system simulation methodology is that it forces us to pay careful attention to the layers of software that will be running on and cooperating with the hardware. In designing a general-purpose parallel machine, it is important to consider not only the processors, memory, and network that form the hardware substrate, but also the operating system that must somehow manage the hardware resources, the parallel libraries required to present an interface to the machine that is both efficient and transparent, and finally the parallel applications themselves which are built on these libraries (Figure 1-1). During the course of this thesis we will have occasion to discuss each of these important aspects of system design.

Figure 1-1: The components of a general purpose parallel computer

-

<sup>&</sup>lt;sup>1</sup> This research was conducted as part of Project Aries (http://www.ai.mit.edu/projects/aries). Hamal is the nickname for Alpha Arietis, one of the stars of the Aries constellation.

### 1.3 Contributions

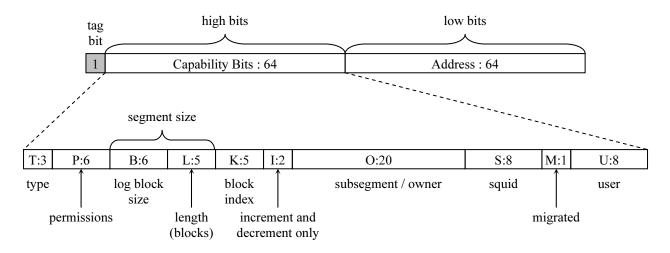

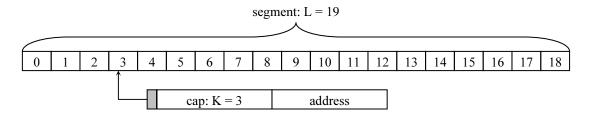

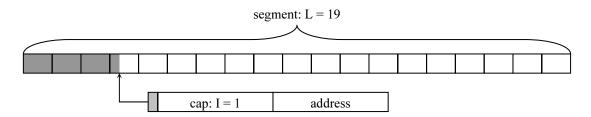

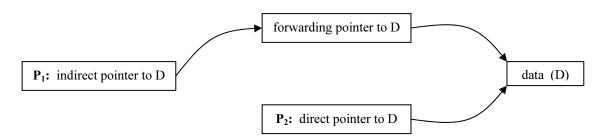

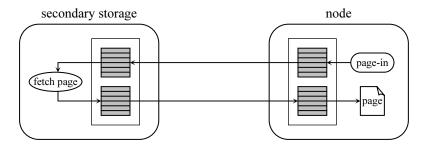

The first major contribution of this thesis is the presentation of novel memory system features to support a scalable, efficient parallel system. A capability format is introduced which supports pointer arithmetic and nearly-tight object bounds without the use of capability or segment tables. We present an implementation of *sparsely faceted arrays* (SFAs) [Brown02a] which allow distributed objects to be allocated with minimal overhead. SFAs are contrasted with *extended address partitioning*, a technique that assigns a separate 64-bit address space to each node. We describe a flexible scheme for synchronization within the memory system. A number of augmentations to DRAM are proposed to improve system efficiency including virtual address translation, hardware page management and memory events. Finally, we show how to implement forwarding pointers [Greenblatt74], which allow references to one memory location to be transparently forwarded to another, without suffering the high costs normally associated with aliasing problems.

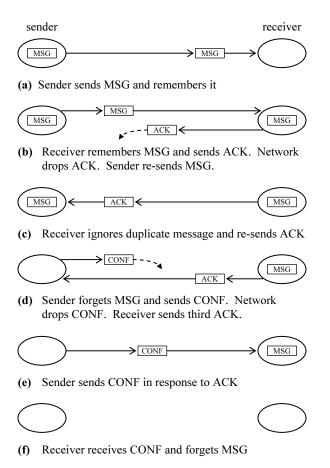

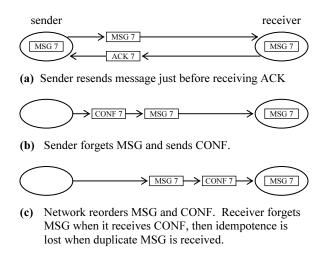

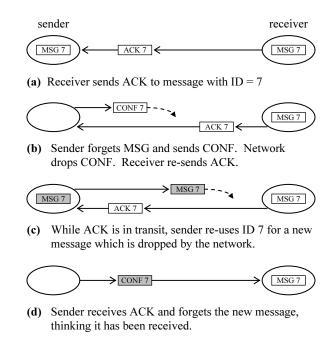

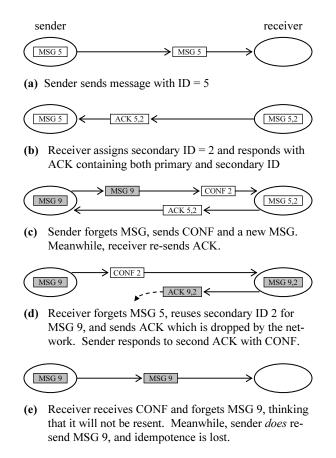

The second contribution is the presentation of a lightweight end-to-end messaging protocol, based on a protocol presented in [Brown01], which guarantees message delivery and idempotence across a discarding network. We describe the protocol, outline the requirements for correctness, and perform simulations to determine optimal implementation parameters. A simple yet accurate analytical model for the protocol is developed that can be applied more broadly to any fault-tolerant messaging protocol.

Our third and final major contribution is the complete description and evaluation of a general-purpose shared-memory parallel computer. The space of possible parallel machines is vast; the Hamal architecture provides a design point against which other general-purpose architectures can be compared. Additionally, a discussion of the advantages and shortcomings of the Hamal architecture furthers our understanding of how to build a "good" parallel machine.

A number of minor contributions are made as we weave our way through the various aspects of hardware and software design. We develop an application-independent hash function with good collision avoidance properties that is easy to implement in hardware. Instruction cache *miss bits* are introduced which reduce miss rates in a set-associative instruction cache by allowing the controller to intelligently select entries for replacement. A systolic array is presented for maintaining least-recently-used information in a highly associative cache. We describe an efficient C++ framework for cycle-based hardware simulation. Finally, we introduce *dynamic sequence partitioning* for reproducibly generating good pseudo-random numbers in multithreaded applications where the number of threads is not known in advance.

#### 1.4 Omissions

The focus of this work is on scalability and memory integration. A full treatise of general purpose parallel hardware is well beyond the scope of this thesis. Accordingly, there are a number of important areas of investigation that will not be addressed in the chapters that follow. The first of these is processor fault-tolerance. Built-in fault-tolerance is essential for any massively parallel machine which is to be of practical use (a million node computer is an excellent cosmic ray detector). However, the design issues involved in building a fault-tolerant system are for the most part orthogonal to the issues which are under study. We therefore restrict our discussion of fault-tolerance to the network messaging protocol, and our simulations make the simplifying assumption of perfect hardware. The second area of research not covered by this work is power. While power consumption is certainly a critical element of system design, it is also largely unre-