Malleable Architectures for Adaptive Computing

MIT9904-04

Start date: 07/99

MIT LCS

Hiroshi Sawada

NTT

| Research Projects |  |

Malleable Architectures for Adaptive ComputingMIT9904-04 Start date: 07/99 |

Arvind, Larry Rudolph, and Srinivas Devadas MIT LCS Hiroshi Sawada NTT |

Project summary |

|

A revolutionary technology for designing hardware and firmware from high-level specifications.

Project description |

|

Neither general-purpose microprocessors nor digital signal processors meet all the needs of intelligent personal devices, multimedia players and recorders, and advanced communication applications. Designing special purpose chips for each application is too expensive to be a feasible solution. It is possible that a large reconfigurable device with appropriate tools and infrastructure may be the solution. We are investigating a revolutionary technology for designing hardware and firmware from high-level specifications. The approach is to synthesize "malleable" processors, with application specific instruction sets, into million-gate FPGAs. The instruction sets of the processors are tailored to each application so as to significantly improve either the performance or the power dissipated during the execution of the application. Synthesis of instruction sets is made possible by the development of an architecture exploration system for programmable processors. This technology can dramatically reduce the time to market in sectors where the standards are changing too quickly or where functionality evolution is too rapid for traditional hardware design. |

Demos, movies and other examples |

|

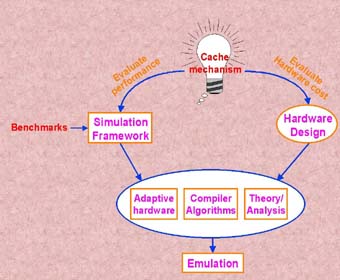

A processor is considered malleable if its resources can be easily adapted to the needs of the operating environment. As a first step, we have proposed a malleable caching mechanism. Depending on the workload, the cache can be dynamically partitioned to support various usage patterns. For example, input and output data streams, like the ones that occur for multimedia and signal processing applications, can make use of the cache without polluting other data items in the cache. A malleable cache will simply allocate separate partitions for stream data. We have built an evaluation environment that permits exploration of new cache replacement policies and resource allocation schemes. |

The principal investigators |

Presentations and posters |

Publications |

"Hardware Synthesis from Term Rewriting Systems", James C. Hoe and Arvind, In Proceedings of VLSI'99, Lisbon, Portugal, December 1999. Also published as CSG-Memo-412A. ![]()

"Using Term Rewriting Systems to Design and Verify Processors", Arvind

and Xiaowei Shen, In IEEE Micro Special Issue on Modeling and Validation of Microprocessors, May/June 1999. Also published as CSG-Memo-419. ![]()

"Scheduling and Synthesis of Operation-Centric Hardware Descriptions", James C. Hoe and Arvind, CSG-Memo-426, November, 1999.

"Deriving Superscalar Microarchitectures from Pipelined Microarchitectures", James C. Hoe and Arvind, CSG-Memo-424, June 1999.

Memory Models:

"Commit-Reconcile and Fences (CRF): A New Memory Model for Architects and Compiler Writers", Xiaowei Shen, Arvind and Larry Rudolph, In Proceedings of the 26th International Symposium on Computer Architecture, Atlanta, Georgia, May 1999. Also published as CSG-Memo-413. ![]()

"CACHET: An Adaptive Cache Coherence Protocol for Distributed Shared-Memory Systems", Xiaowei Shen, Arvind and Larry Rudolph, In Proceedings of the 13th ACM SIGARCH International Conference on Supercomputing, Rhodes, Greece, June 1999. Also published as CSG-Memo-414. ![]()

"Improving the Java Memory Model Using CRF", Jan-Willem Maessen, Arvind and Xiaowei Shen, Submitted to PLDI 2000. Also published as CSG-Memo-428. ![]()

Malleable Caches:

"Application-Specific Memory Management for Embedded Systems", Derek Chiou, Prabhat Jain, Srinivas Devadas and Larry Rudolph, CSG-Memo-427, November 1999. ![]()

"Dynamic Cache Partitioning via Columnization", Derek Chiou, Prabhat Jain, Srinivas Devadas and Larry Rudolph, CSG-Memo-430, November 1999. ![]()

Proposals and progress reports |

Proposals:

NTT Bi-Annual Progress Report, July to December 1999:

NTT Bi-Annual Progress Report, January to June 2000:

NTT Bi-Annual Progress Report, July to December 2000:

NTT Bi-Annual Progress Report, January to June 2001:

NTT Bi-Annual Progress Report, July to December 2001:

NTT Bi-Annual Progress Report, January to June 2002:

For more information |